#### Master's thesis

F3

Faculty of Electrical Engineering Department of Measurement

# Fast multi-channel data acquisition system for radio-astronomy receiver

Jakub Kákona Aircraft and Space Systems

June 2014

http://petr.olsak.net/ctustyle.html Supervisor: Ing. Martin Matoušek, Ph.D.

### **Acknowledgement** / **Declaration**

| Prohlašuji, že jsem předloženou         |

|-----------------------------------------|

| práci vypracoval samostatně a že jsem   |

| uvedl veškeré použité informační zdroje |

| v souladu s Metodickým pokynem o do-    |

| držování etických principů při přípravě |

| vysokoškolských závěrečných prací.      |

V Praze dne 12. 5. 2014

.....

iii Draft: 5. 5. 2014

### **Abstrakt** / **Abstract**

**Klíčová slova:** Radioastronomie, digitalizace signálu, A/D konverze

**Překlad titulu:** Rychlý vícekanálový systém sběru dat pro radioastronomický přijímač

**Keywords:** ADC interface, radioastronomy, signal digitalisation

iv Draft: 5. 5. 2014

### / Contents

| <b>1</b> Introduction                 |

|---------------------------------------|

| 1.1 Current radioastronomy            |

| problems1                             |

| 1.2 Modern Radio astronomy            |

| receiver2                             |

| 1.2.1 Observation types2              |

| 1.3 Required receiver parameters3     |

| 1.3.1 Sensitivity and noise           |

| number3                               |

| 1.3.2 Dynamic range3                  |

| 1.3.3 Bandwidth3                      |

| <b>2</b> Trial design                 |

| 2.1 Required parameters4              |

| 2.2 Sampling frequency4               |

| 2.3 System scalability 4              |

| 2.3.1 Differential signalling5        |

| 2.3.2 Phase matching 5                |

| 2.4 System description5               |

| 2.4.1 Frequency synthesis5            |

| 2.4.2 Signal cable connectors 6       |

| 2.4.3 Signal integrity re-            |

| quirements6                           |

| 2.4.4 ADC modules design6             |

| 2.4.5 ADC selection                   |

| 2.4.6 ADC modules interface 8         |

| 2.4.7 Output data format8             |

| 2.5 Achieved parameters8              |

| 2.5.1 Data reading and                |

| recording9                            |

| 2.5.2 ADC module parame-              |

| ters 11                               |

| <b>3 Example of usage</b>             |

| 3.1 Basic interferometer station 13   |

| 4 Proposed final system 15            |

| 4.1 Custom design of FPGA             |

| board 15                              |

| 4.2 Parralella board computer 15      |

| 4.3 GPU based computational           |

| system                                |

| 5 Conclusion                          |

| 5.1 Possible future improvements . 17 |

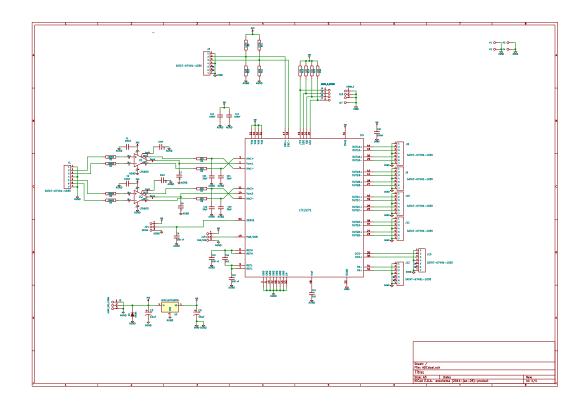

| A Circuit diagram of ADCdu-           |

| al01A module                          |

| B Circuit diagram of FMC2DIFF         |

| <b>module</b> 20                      |

### Tables / Figures

| 1.1. | Dynamic range versus bit |

|------|--------------------------|

|      | depth3                   |

| 2.1. | Available ADC types8     |

| 2.1. | Used miniSAS cable       | . 7 |

|------|--------------------------|-----|

| 2.3. | VITA57 board geometry    | .9  |

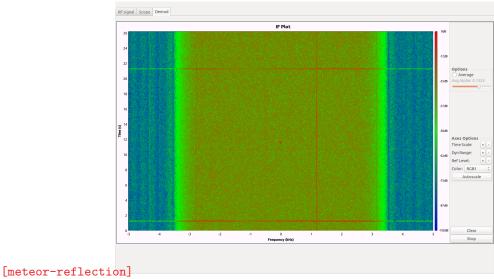

| 3.1. | Meteor reflection        | 13  |

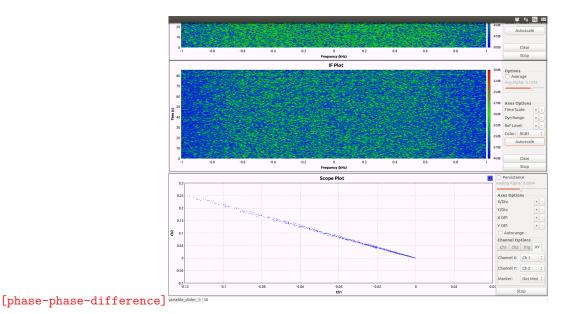

| 3.2. | Phase difference         | 13  |

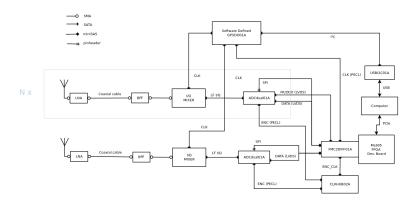

| 3.3. | Receiver block schematic | 14  |

| 4.1. | NVIDIA Jetson TK1 Devel- |     |

|      | opment Kit               | 16  |

vi Draft: 5. 5. 2014

## Chapter 1 Introduction

#### 1.1 Current radioastronomy problems

From a radioastronomer's point of view it is important that radioastronomy focuses its interest primarily on natural signals originating in the surrounding universe. It does not pay much attention to the man-made signals created by our civilisation.

However, it is due to these artificial signals, that the current radioastronomy faces a disturbing problem. The problem arises from the fact, that there are so many terrestrial transmitters currently active and all of them are sources of a dense signal mixture which can cause trouble not only to radioastronomers.

As a consequence, there already exist effort to control the radiofrequency spectrum. As result of attempts to control the radiofrequency spectrum, the frequency allocation table was created. <sup>1</sup>) Radio-frequency allocation table table contains special bands allocated to radioastronomy use. However, for many reasons these bands are not clean enough to be used directly in radioastronomy observations. As a result, we cannot work in the same way as had the radioastronomers in the very beginnings of radioastronomy. Many experiments, namely Cosmic microwave background detection or pulsar detection, cannot be nowadays realised in their original forms with satisfactory results.

Supporting evidence of such effect is RadioJOVE project. NASA engineers who originally created the RadioJOVE project had a great idea. The RadioJOVE project brought an opportunity for creating a publicly available, cheap radioastronomy receiver. However, they used an old-fashioned construction design which, on one hand, can operate in harsh environments like deserts, but on the other it simply did not meet the criteria that would make it possible to be used in modern civilisation, as we know it in Europe. The source of its dysfunction is a presence of strong radiofrequency interferences. These interferences are orders of magnitude stronger than Jupiter decametric emissions, whose detection was the main aim of the RadioJOVE project. From what we have already seen in the light pollution mitigation pursuit, there is only a small chance to radically improve the situation in radiofrequency spectrum.

The only way to overcome this problem is to search for new methods of radioastronomy observations. New methods which allows us to work without completely clear radiofrequency bands and which allow us to see the surrounding universe even despite the existence of man-made radiofrequency interference mixture. One solution is to use already known natural radio frequency signals parameters. Natural signals usually have different signal properties than local interference. Natural objects do not have problems with transmission in bandwidths of tens of megahertz in sub 100 MHz bands. These objects are usually far away and the same signal could be received at almost half of the Earth globe without any significant differences. On the other hand, it is obvious that signals with such parameters have some drawbacks, namely in the reception power. The

1) http://www.ukaranet.org.uk/basics/frequency\_allocation.htm

reception power of radioastronomical object is 1e9 smaller than signal power received from a typical broadband radio transmitter.

From the above mentioned facts concerning the natural radio signals we can conclude that modern requirements imposed on a radioastronomy receiver are completely different from the requirements existing back in the history. Radioastronomy is no longer limited by an access to electronic components, today it is rather limited by the everywhere presence of electronic.

#### 1.2 Modern Radio astronomy receiver

In the beginnings of radioastronomy, the receivers were constructed as simple stations with single antenna or multi antenna array with fixed phasing. This approach was used because of the existing limits of electronic components and technologies. The main challenges of those times were the problem of noise number and low sensitivity, both present due to the poor characteristics of active electronic components such as transistors and vacuum tubes.

Most of the present-day operating radioastronomy equipment has been constructed in similar manner. It was produced usually shortly after the WWII or during The Cold War as a part of military technology.

Today we have an access to components having quality, repeatability and price completely different from the components accessible by previous generation of radioastronomers. That is why we can develop better radioastronomical equipment, powerful enough to make new astronomical discoveries possible.<sup>1</sup>)

We have the capacities necessary to develop a receiver which will have wide bandwidth, high Third-order intercept point and preferably an option for phase and frequency locking to other receivers located at another radioastronomical site at Earth. Currently there exist several receivers with the above-mentioned parameters, for example USRP2, USRP B210 or HackRF and all are commercially available. However all of them lack scalability and have high prices. It is exactly the scalability and redundancy that are the main requirements of noise reduction algorithms.

New radio astronomy systems such LOFAR are explicit examples of the scalability and redundancy approach. LOFAR has completely different and novel structure developed to solve the problems of radioastronomy signal reception. It exclusively uses multi antenna arrays and mathematical algorithms for signal handling. Radio signals recorded by LOFAR can be used in multiple ways: radio images can be computed (if sufficient cover of u/v plane is achieved), radiation intensity can be measured, spectrum can be analysed for velocity measurement, etc.

#### 1.2.1 Observation types

Current radioastronomy knows several types of observations.

- Spectral observations

- Intensity observations

- Velocity observations

All of them prefer high frequency resolution and stability. Wide observation bandwidth in hundreds of MHz is usually desirable for easier differentiation of source types.

Most of astronomy-related discoveries in the last fifty years came from radioastronomy.

#### 1.3 Required receiver parameters

The novel approach of receiver construction described above goes hand-in-hand with new requirements on receiver parameters as well. Currently no additional attempts to improve the signal-to-noise ratio on single antenna are performed. There are however other parameters requested nowadays.

#### ■ 1.3.1 Sensitivity and noise number

Sensitivity and noise number are parameters that are tied together, but multi antenna and multi-receiver arrays force the price of receiver to be kept at minimal value. This implies that the sensitivity and noise number have to be at least so good in the detection (signal /noise ¿ 1 ) of an observed object, that it would be detected on the majority of receivers connected to an observation network.

#### ■ 1.3.2 Dynamic range

Dynamic range represents a huge problem of current radioastronomical receivers. This parameter is enforced by everywhere present humans made EMI radiation on RF frequencies. The modern radio astronomy receiver must not be saturated by this high levels of signals but still needs to have enough sensitivity to see faint signals from natural sources. Dynamic range is limited either by the construction of analogue circuitry in receiver or by the digitalisation unit. The maximal theoretical dynamic range of ADC could be estimated from ADC bit depth using a following formula ??

$$D.R.(dB) = 20 * log(2^n)$$

The formula ?? gives values shown in table below 1.1.

| ADC Bits | Dynamic range [dB] |

|----------|--------------------|

| 8        | 48                 |

| 10       | 60                 |

| 12       | 72                 |

| 14       | 84                 |

| 16       | 96                 |

| 24       | 144                |

[ADC-dynamic-range]

Table 1.1. Standard bit depths of ADC and its theoretical dynamic range.

#### 1.3.3 Bandwidth

Historically, the parameter of bandwidth in radioastronomical receiver used to be within the kilohertz range. Small bandwidth was acceptable because observations were processed directly by listening or by paper chart intensity recorder. Chart recorder integrated energy of signal over defined small bandwidth which was suitable for detecting the intensity variance of microwave background. No wideband transmitters existed in that era (except for TV transmitters) and tuning to other neighbouring frequency was easy as they were mostly vacant. Parallel observations from several places were unnecessary as well because the electromagnetic conditions were nearly same at all locations.

The system requires proper handling of huge amounts of data.

Professional astronomers use proprietary digitalisation units http://arxiv.org/abs/1305.3550 or by multichannel sound cadrd on amateur levels http://fringes.org/

## Chapter 2 Trial design

The whole design of radioastronomy receiver digitalization unit is constructed to be used in a wide range of applications and tasks related to digitalisation of signal from radioastronomy receivers. A good illustrating problem for its use is a signal digitalisation from multiple antenna arrays. This design will eventually become a part of MLAB Advanced Radio Astronomy System.

#### 2.1 Required parameters

Wide dynamical range and high IP3 are desired. The receiver must accept wide dynamic signals because a typical radioastronomical signal has a form of a weak signal covered by a strong man-made noise.

Summary of main required parameters follows

- Dynamical range better than 80 dB

- Phase stability between channels

- Noise (all types)

- Sampling jitter better than 100 metres

- Support for any number of receivers in range 1 to 8

#### 2.2 Sampling frequency

Sampling frequency is limited by the technical constrains in the trial design. This parameter is especially limited by the sampling frequencies of analog-to-digital conversion chips available on the market and interface bandwidth. Combination of the required parameters – dynamic range requiring at least 16bit and a minimum sampling frequency of 1 MSPS leads to need of high end ADC chips which does not support such low sampling frequencies at all. Their minimum sampling frequency is 5 MSPS.

We calculate minimum data bandwidth data rate for eight receivers, 2 bytes per sample and 5MSPS as 8\*2\*5e6 = 80 MB/s. Such data rate is at the limit of real writing speed o classical HDD and it is almost double of real bandwidth of USB 2.0 interface.

#### 2.3 System scalability

For analogue channels scalability, special parameters of ADC modules are required. Ideally, there should be a separate output for each analogue channel in ADC module. ADC module must also have separate outputs for frames and data output clocks. These parameters allow for conduction at relatively low digital data rates. As a result, the digital signal can be conducted even through long wires.

Clock signal will be handled distinctively in our scalable design. Selected ADC chip are guaranteed to have defined clock skew between sampling and data output clock.

4 Draft: 5, 5, 2014

This allows taking data and frame clocks from the first ADC module only. The rest of the data and frame clocks from other ADC modules can be measured for diagnostic purposes (failure detection, jitter measurement etc.).

This system concept allows for scalability, that is technically limited by a number of differential signals on host side and its computational power. There is another advantage of scalable data acquisition system – an economic one. Observatories or end users can make a choice of how much money are they willing to spent on radioastronomy receiver system. This freedom of choice is especially useful for science sites without previous experience in radioastronomy observations.

#### **2.3.1** Differential signalling

The concept of scalable design requires relatively long circuit traces between ADC and digital unit which captures the data and performs the computations. The long distance between the digital processing unit and the analog-to-digital conversion unit has an advantage in noise retention typically produced by digital circuits. Those digital circuits, such as FPGA or other flip-flops block and circuit traces, usually work at high frequencies and emit wide-band noise with relatively low power. In such cases any increase in a distance between the noise source and analog signal source increase S/N significantly. However, at the same time a long distance brings problems with the digital signal transmission between ADC and computational unit. This obstacle should be resolved more easily in free-space than on board routing. The high-quality differential signalling shielded cables should be used. This technology has two advantages over PCB signal routing. First, it can use twisted pair of wires for leak inductance suppression in signal path and second, the twisted pair may additionally be shielded by uninterrupted metal foil.

#### **2.3.2** Phase matching

For multiple antenna radioastronomy projects, system phase stability is a mandatory condition. It allows precise high resolution imaging of objects.

High phase stability in our scalable design is achieved through centralised frequency generation and distribution with multi-output LVPECL hubs, that have equiphased outputs for multiple devices.

This design ensures that all devices have access to the defined phase and known frequency.

#### 2.4 System description

In this section testing system will be described.

#### **2.4.1** Frequency synthesis

We have used a centralised topology as a basis for frequency synthesis. One precise high-frequency and low-jitter digital oscillator has been used, while other working frequencies have been derived from it by the division of its signal. This central oscillator has a software defined GPS disciplined control loop for frequency stabilisation.<sup>1</sup>) We have used methods of frequency monitoring compensation in order to meet modern requirements

<sup>1)</sup> http://wiki.mlab.cz/doku.php?id=en:gpsdo SDGPSDO design has been developed in parallel to this diploma thesis as a related project, but it is not explicitly required by the diploma thesis.

on radioastronomy equipment which needs precise frequency and phase stability over a wide scale for effective radioastronomy imaging.

Every ADC module will be directly connected to CLKHUB02A module which takes sampling clock signal delivered by FPGA from main local oscillator. This signal should use high quality differential signalling cable – we should use SATA cable for this purpose.

GPSDO design included in data acquisition system has special feature – generates time marks for precise time-stamping of received signal. Timestamps are created by disabling of local oscillator for 100 us as result rectangle click in input signal is created which appears as horizontal line in spectrogram. Timestamps should be seen in image 3.1 (above and below meteor reflection).

Time-marking should be improved in future by digitalisation GPS signal directly with dedicated ADC channel. Datafile then consists samples from channels of radio-astronomy receivers along with GPS signal containing precise time information.

#### **2.4.2** Signal cable connectors

Several widely used and commercially easily accessible differential connectors were considered to be use in our design.

- HDMI

- SATA

- DisplayPort

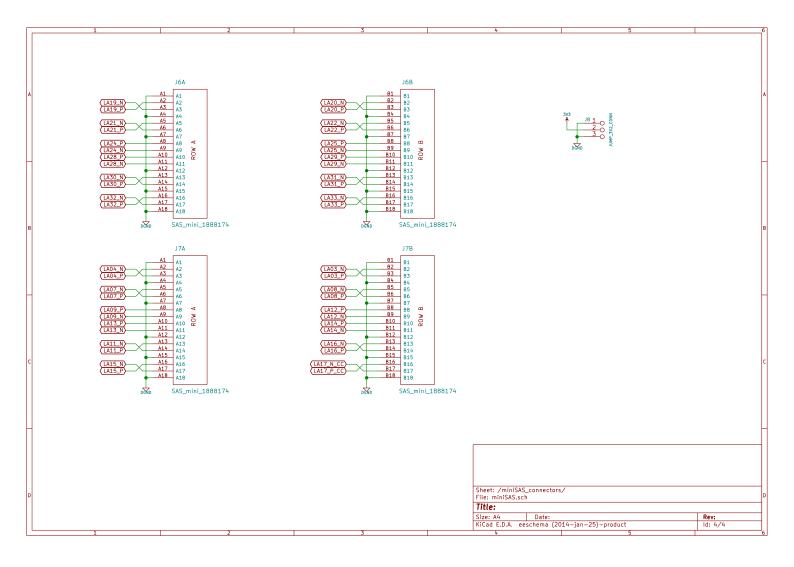

- SAS/miniSAS

At the end, MiniSAS connector was chosen as the best option to be used in connecting together multiple ADC modules. It is compatible with existing SATA cabling systems and aggregates multiple SATA cables to a single connector. It can be seen on the following picture 2.1. A transition between SATA and miniSAS is achieved by SAS to SATA adapter cable which is commonly used in servers to connect SAS controller to multiple SATA hard disc in RAID systems and thus is commercially easily available. The main drawback of miniSAS PCB connectors lies in the fact, that they are manufactured in SMT versions only. The outer metal housing of connector is designed to be mounted using a standard through-hole mounting scheme, a design that unfortunately decreases the durability of the connector.

#### **2.4.3** Signal integrity requirements

We use ADC modules that have DATA clock frequency eight times higher than sampling frequency in single line output mode, implying a 40 MHz output bit rate.

#### 2.4.4 ADC modules design

The ADC modules have a standard MLAB construction scheme with four mounting holes in corners aligned in defined raster.

Data serial data outputs of ADC modules should be connected directly to FPGAs for the basic primary signal processing. The ADC chip used in the modules has a selectable bit width of data output bus and thus the output SATA connectors have signals arranged to contain a single bit from every ADC channel. This creates a signal concept enabling a selection of a proper bus bit-width according to the sampling rate (higher bus bit-width downgrades signalling speed and vice versa.)

In order to connect the above mentioned signalling layout, miniSAS to multiple SATA cable should be used.

Figure 2.1. A type of miniSAS cable similar to used.

A KiCAD design suite had been chosen for PCB layout. However, the version is, despite having integrated CERN Push & Shove routing capability, slightly unstable as it sometimes crushes due to an exception during routing. On the basis of these stability issues, the design had to be saved quite often. On the other hand, compared to commercially available solutions, such as MentorGraphics PADS or Cadence Orcad, the Open-source KiCAD provides an acceptable option and it easily surpasses a widely used Eagle software.

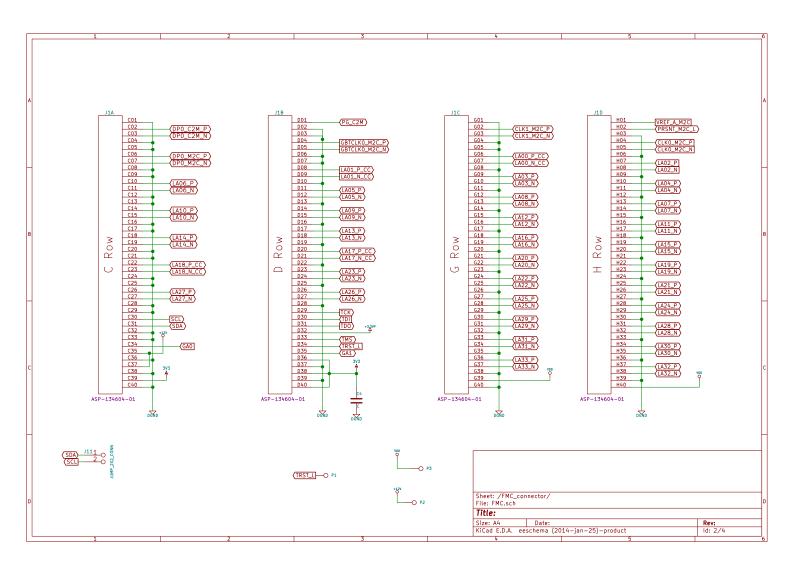

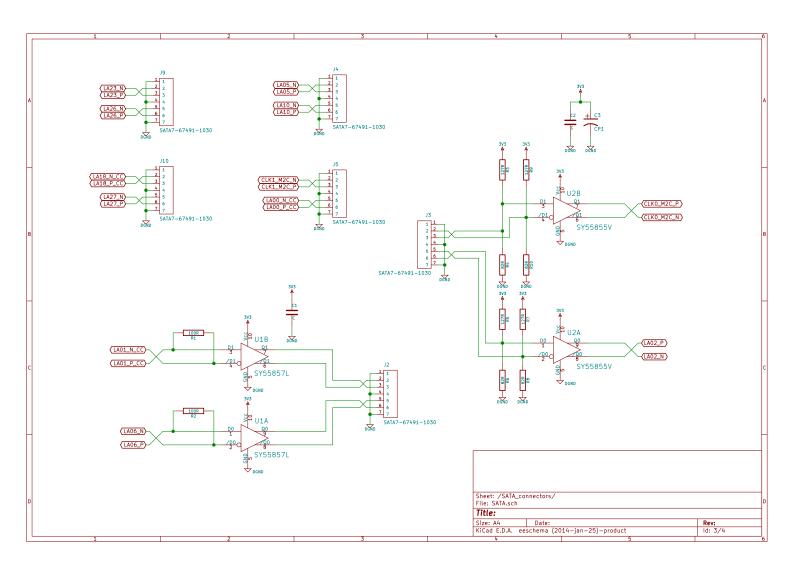

As a part of work on the thesis, new PCB footprints for FMC, SATA a and miniSAS connectors have been designed and were committed to KiCAD github library repository. They are now publicly available on the official KiCAD repository at GitHub.

#### 2.4.5 ADC selection

There exist several ADC signalling formats currently used in communication with FPGA.

- DDR LVDS

- JEDEC 204B

- JESD204A

- Paralel LVDS

- Serdes

- serial LVDS

Because it uses the smallest number of differential pairs, the choice fell on the serial LVDS format. Small number of differential pairs is an important parameter determining the construction complexity and reliability. http://www.ti.com/lit/pdf/snaa110

An ultrasound AFE chip seems to be ideal for this purpose – the chip has integrated both front-end amplifiers and filters. It has a drawback though - it is incapable of

handling differential input signal and has a relatively low dynamic range (as it consists only of 12bit ADC). Because this IO has many ADC channels the scaling is possible only by a factor of 4 receivers (making 8 analogue channels).

If we require a separate output for every analogue channel and a 16bit depth we find that there are only a few 2-Channel simultaneous sampling ADCs currently existing which meet these requirements. We have summarised the ADCs in the following table ??

| ADC Type             | LTC2271 | LTC2190 | LTC2191         | LTC2192 | LTC2193          | LTC2194 | LTC2195 |

|----------------------|---------|---------|-----------------|---------|------------------|---------|---------|

| SNR [dB]             | 84.1    | 77      | 77              | 77      | 76.8             | 76.8    | 76.8    |

| SFDR [dB]            | 99      | 90      | 90              | 90      | 90               | 90      | 90      |

| S/H Bandwidth [MHz]  | 200     |         |                 | 55      | 0                |         |         |

| Sampling rate [MSPS] | 20      | 25      | 40              | 65      | 80               | 105     | 125     |

| Configuration        |         |         |                 | SPI     |                  |         |         |

| Package [ADC-types]  | 52-     | -Lead   | $(7\mathrm{mm}$ |         | $8 \mathrm{mm})$ | QF      | 'N      |

**Table 2.1.** The summary of available ADC types and theirs characteristics.

All parts in this category are compatible with one board layout. Main differences lay in the sampling frequency and signal to noise ratio, with the slowest having a maximum sampling frequency of 20 MHz. However all of them have a minimal sampling frequency of 5 MSPS and all are configurable over a serial interface (SPI). SPI seems to be a standard interface used in high-end ADC chips made by the largest manufacturers (Analog Devices, Linear technology, Texas instruments, Maxim integrated..).

#### 2.4.6 ADC modules interface

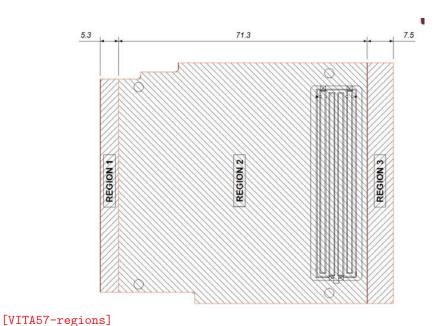

Both of the ADCdual01A modules were connected to FPGA ML605 board trough FMC2DIFF01A adapter board. The design of this adapter module expects the presence of FMC LPC connector and the board is, at the same time, not compatible with MLAB. It is, on the other hand, designed to meet the VITA 57 standard specifications for boards which support region 1 and region 3. VITA 57 regions are explained in the picture 2.3. This industry standard guarantees the compatibility with other FPGA boards that have FMC LPC connectors for Mezzanine Card. Schematic diagram of this adapter board is included in the appendix.

The primary purpose of the PCB is to enable the connection of ADC modules located outside the PC case. (In PC box analog circuits cannot be realised without the use of massive RFI mitigation techniques). Differential signalling connectors should be used for conducting digital signal over relatively long cables. The signal integrity sensitive links (clocks) are equipped with output driver and translator to LVPECL logic for better signal transmission quality.

Several SATA connectors and two miniSAS connectors are populated on this board. This set of connectors allows a connection of any number of ADC modules within the range of 1 to 8. ADC data outputs should be connected to the miniSAS connectors, while other supporting signals should be routed directly to SATA connectors on adapter. Signal configuration used in our trial design is described in the following tables.

#### 2.4.7 Output data format

#### 2.5 Achieved parameters

Figure 2.2. FPGA ML605 development board.

Figure 2.3. Definition of VITA57 regions.

|           |            |       |           | 160k  | oit packet |       |           |       |           |  |

|-----------|------------|-------|-----------|-------|------------|-------|-----------|-------|-----------|--|

| Data name | FRAME      | ADC   | 1 CH1     | ADC   | 1 CH2      | ADC   | 2 CH1     | ADC:  | 2 CH2     |  |

| Data type | uint32     | int16 | int16     | int16 | int16      | int16 | int16     | int16 | int 16    |  |

| Content   | saw signal | t1    | $t_{1+1}$ | t1    | $t_{1+1}$  | t1    | $t_{1+1}$ | t1    | $t_{1+1}$ |  |

Table 2.2. System device /dev/xillybus\_data2\_r data format

#### **2.5.1** Data reading and recording

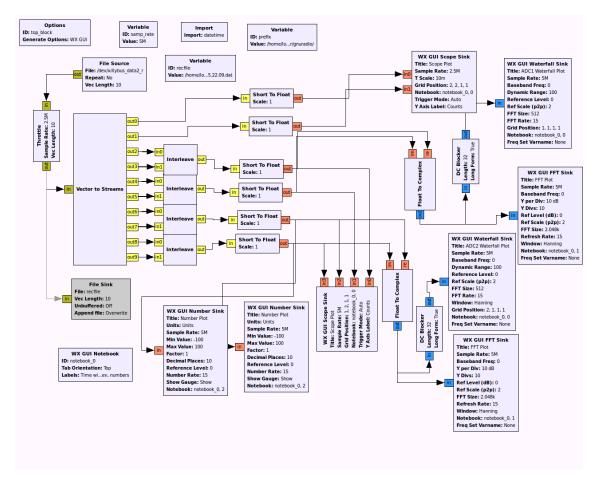

We use Gnuradio software to read the data stream from the ADC drive. Gnuradio suite consist of gnuradio-companion which is a graphical tool for creating signal-flow graphs and generating flow-graph source code. This tool was used to create a basic RAW data grabber to record and interactively view the data stream output from ADC modules.

**Figure 2.4.** An ADC recorder flow graph created in gnuradio-companion.

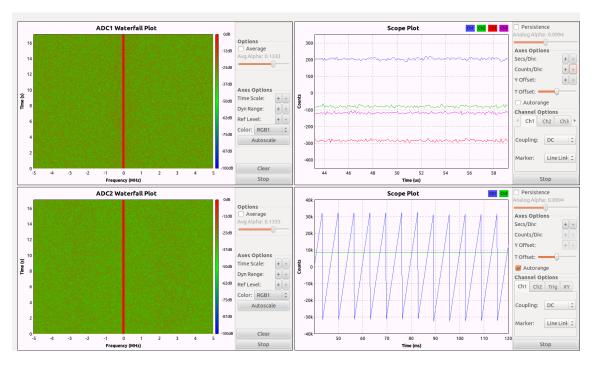

Figure 2.5. User interface window of a running ADC grabber.

Interactive grabber viewer user interface shows live oscilloscope-like time-value display for all data channels and live time-frequency scrolling display (a waterfall view) for displaying the frequency components of the grabbed signal.

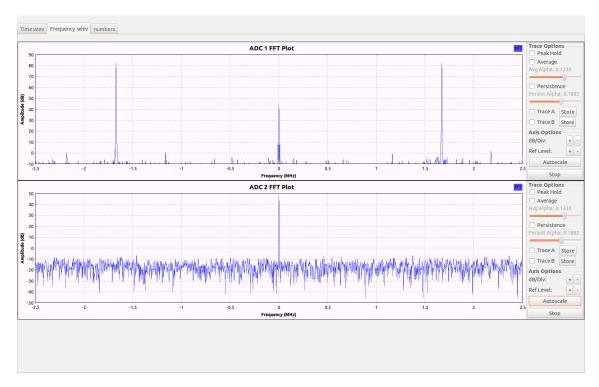

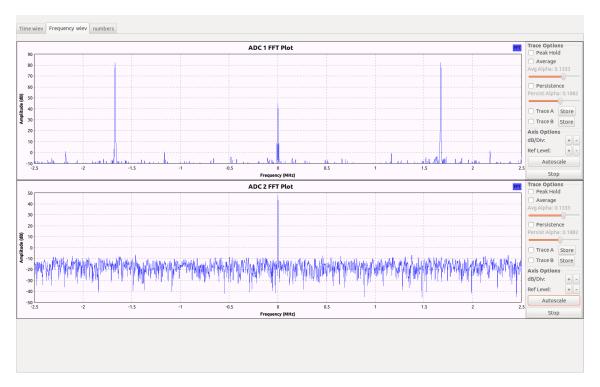

#### **2.5.2** ADC module parameters

Two pieces of ADC modules were completed and tested. The first piece, labeled ADC1, has LTC21190 ADC chip populated with LT660015 front-end operational amplifier. It also has a 1kOhm resistors populated on inputs which gives it an ability of an internal attenuation of input signal. The value of this attenuation A is described by the following formula

$$A = \frac{1580 \times R_1}{R_1 + R_2}$$

Figure 2.6. Sine signal from ADC1 module with LTC21190 and LT6600-5 devices.

ADC1 CH1 maximal input  $705.7~\mathrm{mV}$  LTC2271  $6600125~\mathrm{1k}$  ADC2 CH1 maximal input  $380~\mathrm{mV}$

$$D.R. = N * b*$$

Where is

- N number of receivers

- Mi

#### 2. Trial design

Figure 2.7. Sine signal from ADC1 module with LTC21190 and LT6600-5 devices.

## Chapter 3 Example of usage

#### 3.1 Basic interferometer station

For system evaluation basic interferometry station was constructed.

Figure 3.1. Meteor reflection received by evaluation setup.

Figure 3.2. Demonstration of phase difference between antennas.

#### 3. Example of usage

#### [block-schematic]

Figure 3.3. Complete receiver block schematic of dual antenna interferometric station.

## Chapter 4 Proposed final system

Construction of a final system which is supposed to be employed for real radioastronomy observations will be described. This chapter is mainly a theoretical analysis of data handling systems. Realisation of these ideas might be possible as a part of our future development after we fully evaluate and test the current trial design.

### 4.1 Custom design of FPGA board

In the beginning of the project, a custom design of FPGA interface board had been considered. This FPGA board should include PCI express interface and should sell at lower price than trial design. It should be compatible with MLAB which is further backward compatible with the existing or improved design of ADC modules. For a connection of this board to another adapter board with PCIe we expect a use of a host interface. Thunderbolt technology standard was expected to be used in this PC to PCIe -; FPGA module. Thunderbolt chips are currently available on the market for reasonable prices. However, a problem lies in the accessibility to their specifications, as they are only available for licensed users and Intel has a mass market oriented licensing policy, that makes this technology inaccessible for low quantity production. As a consequence, an external PCI Express cabling and expansion slots should be considered as a better solution.

However, these systems and cables are still very expensive. Take (http://www.opalkelly.com/products/xe as an example, with its price tag reaching 995 USD at time of writing of thesis. Therefore, a better solution probably needs to be found.

#### 4.2 Parralella board computer

#### 4.3 GPU based computational system

A new GPU development board NVIDIA K1, shown in the following picture 4.1, has recently been released. These boards are intended to be used in fields including computer vision, robotics, medicine, security or automotive industry. They have ideal parameters for signal processing for a relatively low price of 192 USD. Unfortunately, they are currently only in pre-order release stage (in April 2014).

[img-NVIDIA-K1]

Figure 4.1. The NVIDIA Jetson TK1 Development Kit https://developer.nvidia.com/jetson-tk1.

## Chapter 5 Conclusion

Special design of scalable data-aquisition system was proposed. This system has parameters

#### 5.1 Possible future improvements

Several ADC module imperfections, such as useless separation of FRAME and DCO signal to two connectors, should be mitigated. And this two signals should be merged to one SATA connector. This modification removes one redundant SATA cable between analog to digital converter nest and between computational unit nest.

## Appendix **A**

### Circuit diagram of ADCdual01A module

## Appendix B Circuit diagram of FMC2DIFF module

|   | 1             | 2             | 3          | 4                                                            |                                       | 5 | б    |

|---|---------------|---------------|------------|--------------------------------------------------------------|---------------------------------------|---|------|

| A | EMC.connector |               |            |                                                              |                                       |   | A    |

|   | FMC.sch       | SATA_connecto | miniSAS_co | nnectors                                                     |                                       |   |      |

|   |               | SAIA.sch      | miniSAS.sc | h                                                            |                                       |   |      |

| В |               |               |            |                                                              |                                       |   | E    |

|   |               |               |            |                                                              |                                       |   |      |

| c |               |               |            |                                                              |                                       |   | c    |

|   |               |               |            | Flank /                                                      |                                       |   |      |

| D | 1             |               | 3          | Sheet: / File: FMC2DIFF.sc  Title: Size: A4 KiCad E.D.A. ees | Date:<br>schema (2014-jan-25)-product | 5 | Rev: |